第一章 单元测试

1、单选题:

目前使用最为广泛的硬件描述语言是( )

选项:

A:C语言

B:汇编语言

C:Verilog HDL

D:Python编程语言

答案: 【Verilog HDL

】

2、单选题:

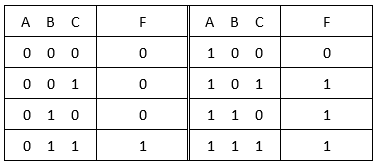

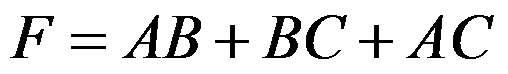

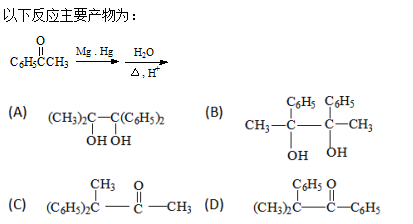

某组合逻辑电路的真值表如下:

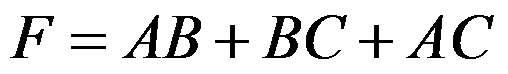

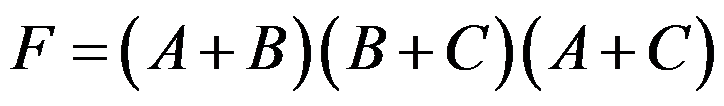

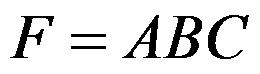

则输出F的表达式为( )

选项:

A:

B:

C:

D:

答案: 【

】

3、单选题:

阅读如下程序:

module myxor(a,b,c);

input a,b;

output c;

assign c=a^b;

endmodule

该程序完成的功能是( )

选项:

A:与门

B:非门

C:或门

D:异或门

答案: 【异或门

】

4、单选题:

下列关于Verilog HDL说法错误的是( )

选项:

A:利用Verilog HDL设计数字系统,可以采取自顶向下的设计思想

B:Verilog HDL语言设计电路时,提供了多种层次抽象的描述

C:Verilog HDL是世界上唯一的硬件描述语言

D:Verilog HDL的设计方法,因为其标准化,所以具有工艺无关性的优点

答案: 【Verilog HDL是世界上唯一的硬件描述语言

】

5、单选题:

下面缩写表示可编程逻辑器件的是( )

选项:

A:EDA

B:ASIC

C:PLD

D:VLSI

答案: 【PLD】

第二章 单元测试

1、单选题:

下列不属于数据流描述的特征的是( )

选项:

A:使用线网类型的变量

B:既可以描述组合逻辑电路又可以描述时序逻辑电路

C:用于描述组合逻辑电路

D:使用连续赋值语句

答案: 【既可以描述组合逻辑电路又可以描述时序逻辑电路

】

2、单选题:

在结构化描述中,调用系统内部门的时候,端口的顺序是( )

选项:

A:输入在前,输出在后

B:输出在前,输入在后

C:只需要填写输入

D:顺序可以任意

答案: 【输出在前,输入在后

】

3、单选题:

条件结构(比如if-else语句)和循环结构(比如for语句)可以用在( )

选项:

A:其他选项均可以

B:结构化描述

C:行为描述

D:数据流描述

答案: 【行为描述

】

4、单选题:

下列关于测试平台的说法,正确的是( )

选项:

A:在测试平台中可以不用调用被测模块

B:在测试平台中只能使用initial语句

C:在测试平台必须给出输入输出端口

D:测试平台的作用是给出测试信号的变化从而得到输出以验证电路的功能

答案: 【测试平台的作用是给出测试信号的变化从而得到输出以验证电路的功能

】

5、单选题:

在某测试平台中有如下语句:

initial begin testa=0;

#10 testa=1;

$stop;

end

下列说法错误的是( )

选项:

A:$stop用于结束仿真过程

B:#50表示延时50个时间单位

C:initial语句用于变量的初始化

D:测试信号testa在上电时值为0,10个时间单位后变为1

答案: 【$stop用于结束仿真过程

】

第三章 单元测试

1、单选题:

在Verilog HDL中,下列标志符不合法的是( )

选项:

A:state0

B:9moon

C:signall

D:Not_Stack_0

答案: 【

】

2、单选题:

关于Verilog HDL中的模块调用,下列说法错误的是( )

选项:

A:在语句“Mydesign design(port1,port2);”中,被调用的模块名称为Mydesign

B:在模块调用时,端口是两个模块联系的通道

C:在模块调用时,必须严格按照模块定义的端口顺序来连接

D:在模块调用时,端口可以采用顺序相对应和形参实参相对应两种方式

答案: 【

】

3、单选题:

下列Verilog HDL语句中,数据类型定义与注释矛盾的是( )

选项:

A:reg [0:3] myreg; //myreg为4位寄存器类型变量

B:reg [15:0] memory; //memory为16位寄存器类型变量

C:wire [3:0] sat; //sat为4位线网类型变量

D:reg [1:5] areg; //areg为4位寄存器类型变量

答案: 【

4、单选题:

行为描述中被赋值的变量必须声明为( )

选项:

A:线网类型

B:参数类型

C:均有可能波

D:寄存器类型

答案: 【

5、单选题:

下列不属于端口类型说明关键字的是( )

选项:

A:output

B:duplex

C:inout

D:input

答案: 【

】

第四章 单元测试

1、单选题:

已知a=1’b1,b=3’b001,那么{a,b}=( )

选项:

A:4’b0011

B:4’b1001

C:3’b001

D:3’b101

答案: 【

】

2、单选题:

已知a=4’b11001,b=4’bx110,则下列计算正确的是( )

选项:

A:a&b=4’bxxxx

B:a&b=4’b0

C:a&&b=1’bx

D:a&&b=1’b1

答案: 【

】

3、单选题:

已知a=4’b1001,则执行下面的语句之后:

reg [5:0] f;

f=a<<2;

变量f的值为( )

选项:

A:6’b000111

B:6’b100111

C:6’b000100

D:6’b100100

答案: 【

】

4、单选题:

已知变量a、b和c的位宽均为4,且a、b的初始值分别为4’b1001和4’b1010,程序中有如下语句:

always @(a or b)

begin b<=a;

c<=b;

end

则在上电执行后,变量c的值为( )

选项:

A:4’b1001

B:4’bxxxx

C:4’b10xx

D:4’b1010

答案: 【

】

5、单选题:

关于阻塞性过程赋值和非阻塞性过程赋值,下列说法正确的是( )

选项:

A:描述组合逻辑电路时,建议采用非阻塞性过程赋值

B:在Verilog HDL语句块内部,非阻塞性过程赋值的语句是并行执行的

C:描述时序逻辑电路时,建议采用阻塞性过程赋值

D:阻塞性过程赋值采用“<=”符号,非阻塞性过程赋值采用“=”符号

答案: 【

第五章 单元测试

1、单选题:

已知a=4’bx010,则执行下面语句后,

if(a>2) out=1;

else out=0;

out的值为( )

选项:

A:x

B:1

C:无法确定

D:0

答案: 【

】

2、单选题:

在下面的语句中,

always @(a or b)

if(a>b) q<=1;

信号q经过综合后会形成( )

选项:

A:门电路

B:触发器

C:锁存器

D:连线资源

答案: 【

】

3、单选题:

某Verilog HDL的程序部分如下:

reg [7:0] areg;

always @(in) begin num=0;

for(areg=in;areg;areg=areg>>1)

if(areg[0]==1) num=num+1;

end

若输入in=8’b10110011,则程序结束后,num的值为( )

选项:

A:5

B:3

C:2

D:4

答案: 【

】

4、单选题:

仿真时执行下面的初始化语句:

initial forever #30 clk=~clk;

执行完成后,得到的clk信号为( )

选项:

A:周期为30的方波

B:一直为x

C:一直为0

D:周期为60的方波

答案: 【

】

5、单选题:

某条件语句如下,已知变量count的值为4’b0011:

if(count<5) out=1;

else if(count<7) out=2;

else out=3;

则执行条件语句后输出out的值为( )

选项:

A:2

B:3

C:x

D:1

答案: 【

】

第六章 单元测试

1、单选题:

若a=9,执行下面语句;

$display(“Current value = %0b, a=%0d”, a,a);

显示的结果为( )

选项:

A:Current value = 1001, a=9

B:Current value = 0b1001, a=0d9

C:1001,9

D:Current value = 1001, a=09

答案: 【

】

2、单选题:

若时间尺度定义为:`timescale 10ns/100ps,则下列说法正确的是( )

选项:

A:时间精度为100ps

B:时间精度为10ns

C:时间单位为1ns

D:时间单位为100ps

答案: 【

3、单选题:

某Verilog HDL的程序部分如下:

always @(a or b)

out=a&b;

always @(b or c)

out=b^c;

已知a、b、c和out的位宽均为1,且a=c=1’b0,b=1’b1,则( )

选项:

A:语法有误

B:out=1’b0

C:out=1’b1

D:1’bx

答案: 【

】

4、单选题:

在Verilog HDL中,关于任务和函数,下列说法错误的是( )

选项:

A:一个任务可以调用别的任务和函数

B:任务和函数的定义和调用都在一个模块内部

C:任务和函数内部可以包含定时控制描述

D:一个函数至少需要一个输入,产生一个返回值

答案: 【

】

5、单选题:

某Verilog HDL的程序部分如下:

module example(a,b,c,d,e);

input a,b,c,d;

output reg e;

always @(*)

e=(a&b) ^c;

endmodule

在该程序中,“*”号表示的敏感变量列表中的敏感变量包括( )

选项:

A:a

B:a,b,c,d

C:a,b

D:a,b,c

答案: 【

】

第七章 单元测试

1、判断题:

QuartusⅡ作为一种可编程逻辑的设计环境,是由Xilinx公司开发的。( )

选项:

A:错

B:对

答案: 【】

2、判断题:

ModelSim是一款优秀的硬件描述语言仿真软件。( )

选项:

A:对

B:错

答案: 【】

3、单选题:

在QuartusⅡ软件环境中,新建项目之后采用Verilog HDL输入,应该选择新建的源文件类型是( )

选项:

A:AHDL file

B:EDIF file

C:VHDL file

D:Verilog HDL file

答案: 【

】

4、单选题:

在QuartusⅡ软件环境中,设置引脚端口的工具叫( )

选项:

A:Pin Planner

B:RTL Simulation

C:Assignment Editor

D:Programmer

答案: 【

】

5、单选题:

①功能仿真;②代码编写;③优化;④管脚配置

在QuartusⅡ设计工具中,可编程逻辑器件的设计流程为:原理图或HDL输入→综合→______→______→下载→硬件调试。空缺中应填的分别是( )

选项:

A:①④

B:③①

C:③⑤

D:②④

答案:

】

第八章 单元测试

1、单选题:

在Verilog HDL中,直接利用乘法运算符描述的乘法器,经过综合之后生成的乘法器属于( )

选项:

A:串行乘法器

B:移位相加乘法器

C:超前进位乘法器

D:并行乘法器

答案: 【

】

2、单选题:

在Verilog HDL中,利用加法运算符可以描述并行加法器。现在要完成一个纯组合逻辑电路的加法器,下列描述正确的是( )

选项:

A:always @(a or b)

{cout,sum}=a+b;

B:always @(posedge clk)

{sum,cout}=a+b;

C:always @(posedge clk)

{cout,sum}=a+b;

D:always @(a or b)

{sum,cout}=a+b;

答案: 【

】

3、单选题:

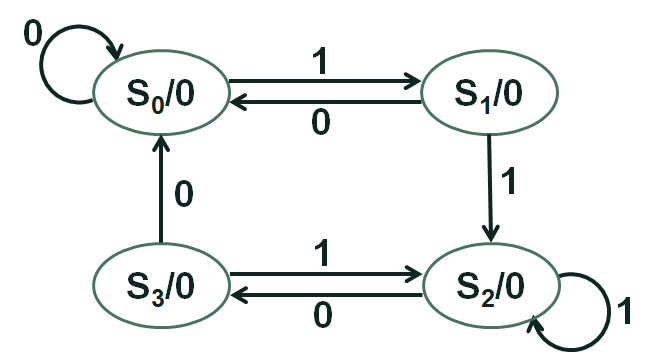

在Verilog HDL中,为了完成具有优先功能的四-二编码器(功能表如图所示),

部分程序如下:

always @(in3,in2,in1,in0)

________

4’b0001:{F1,F0}=2’b00;

4’b001x:{F1,F0}=2’b01;

4’b01xx:{F1,F0}=2’b10;

4’b1xxx:{F1,F0}=2’b11;

default:{F1,F0}=2’bxx;

endcase

空格处应填( )

选项:

A:case(in3,in2,in1,in0)

B:case({in3,in2,in1,in0})

C:casex({in3,in2,in1,in0})

D:casex(in3,in2,in1,in0)

答案: 【

】

4、单选题:

某Verilog HDL的程序如下:

module top(A,B,Con,out);

input A,B,Con;

output out;

assign out=(Con)?A:B;

endmodule

该程序描述的模块功能是( )

选项:

A:一位数值比较器

B:二选一的多路选择器

C:四选一的多路选择器

D:半加器

答案: 【

】

5、单选题:

在Verilog HDL中描述组合逻辑电路,下列说法错误的是( )

选项:

A:行为描述只能用来描述时序逻辑电路

B:如果知道电路输出的表达式,可以采用数据流描述

C:数据流描述只能用来描述组合逻辑电路

D:如果知道电路原理图,可以采用结构化描述

答案: 【

】

第九章 单元测试

1、单选题:

关于时序逻辑电路的描述,下列说法正确的是( )

选项:

A:时序逻辑电路的描述中,赋值语句一定要采用非阻塞性过程赋值

B:对于时序逻辑电路的描述,电平触发和边沿触发的效果一样

C:时序逻辑电路中的触发器若没有初始化,则其值为不定值

D:描述时序逻辑电路的功能时,既可以采用initial语句,也可以采用always语句

答案: 【

】

2、单选题:

下列表示采用时钟上升沿触发且低电平异步复位的代码描述是( )

选项:

A:always @(posedge clk or posedge rst)

if(rst) out<=0;

B:always @(posedge clk or rst)

if(!rst) out<=0;

C:always @(posedge clk or negedge rst)

if(rst) out<=0;

D:always @(posedge clk or negedge rst)

if(!rst) out<=0;

答案: 【

】

3、单选题:

某Verilog HDL的分频器程序部分如下:

reg [3:0] count;

always @(posedge clk or negedge rst)

if(!rst) count<=0;

else if(count==9) count<=0;

else count<=count+1;

assign newclk=count[3];

若系统时钟clk的频率为50MHz,则分频后的时钟newclk的频率为( )

选项:

A:3.125MHz

B:12.5MHz

C:6.25MHz

D:25MHz

答案: 【

】

4、单选题:

某Verilog HDL的计数器程序部分如下:

reg ____ count;

always @(posedge clk or negedge rst)

if(!rst) count<=0;

else if(count==_____) count<=0;

else count<=count+1;

为了完成模24(从0数到23)的计数,上面程序的空格处应该填( )

选项:

A:[4:0]和5’b11000

B:[5:0]和6’b24

C:[4:0]和5’b10111

D:[4:0]和5’b23

答案: 【

】

5、单选题:

某Verilog HDL的程序部分如下:

reg [3:0] shift;

always @(posedge clk or negedge rst)

if(!rst) shift<=4’d8;

else shift<={shift[2:0],shift[3]};

复位之后,shift的初始值为4’d8,然后经过三次移位操作,shift的值为( )

选项:

A:4’d4

B:4’d2

C:4’d1

D:4’d8

答案: 【

】

第十章 单元测试

1、判断题:

Moore类型的有限状态机的输出不仅取决于当前的状态,还与当前的输入有关。( )

选项:

A:错

B:对

答案: 【】

2、判断题:

有限状态机是由寄存器组和组合逻辑构成的硬件时序电路。( )

选项:

A:对

B:错

答案: 】

3、单选题:

有限状态机描述的步骤包括:

①模块定义和输入输出端口声明; ②编写always语句;

③选择合适的状态编码; ④定义状态寄存器变量;

正确的描述顺序是( )

选项:

A:①④③②

B:①②③④

C:①④②③

D:①③②④

答案: 【

】

4、单选题:

下列不属于有限状态机的优点的是( )

选项:

A:利用有限状态机设计的电路具有最佳的速度和功耗

B:在高速运算和控制方面,有限状态机比一般的CPU有优势

C:有限状态机设计方案相对固定,结构模式简单

D:有限状态机容易构成性能良好的同步时序逻辑模块

答案: 【

】

5、单选题:

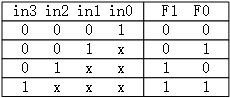

为了完成如下图所示的状态机:

在状态机的程序编写过程中,采用自然码编码和独热码编码,定义的状态寄存器变量的位宽通常分别为( )

选项:

A:2位、4位

B:2位、5位

C:4位、4位

D:4位、5位

答案: 【

】

第十一章 单元测试

1、单选题:

关于电路的逻辑综合,下列说法错误的是( )

选项:

A:编写Verilog HDL代码的时候,要保证采用的语句的可综合性

B:综合可以验证电路的功能是否正确

C:在综合前后,要进行仿真

D:编写Verilog HDL代码的时候,要注意培养可综合风格的代码编写方式

答案: 【

】

2、单选题:

在编写高效的Verilog HDL程序的过程中,需要考虑提高资源利用率减少功率(即面积优化),以及提高运行速度(即速度优化)。下列属于面积优化的是( )

选项:

A:设计并行电路

B:资源共享

C:设计同步电路

D:流水线设计

答案: 【

】

3、单选题:

某Verilog HDL的程序部分如下:

always @(a or b or c)

if(a==b) d=c;

else if(a&~b) d=~c;

该程序经过综合生成电路,下列说法不正确的是( )

选项:

A:为了避免锁存器的产生,需要定义条件语句的所有可能的选项

B:该部分语句经过综合生成的电路是纯组合逻辑电路

C:if-else语句经过综合之后一般生成二选一的多路选择器

D:该部分语句经过综合将产生锁存器

答案: 【

4、单选题:

在Verilog HDL中,有些语句可综合,有些语句不可综合,下列属于可综合语句的是( )

选项:

A:延时描述语句,比如#50

B:没有书写default选项的case语句

C:循环次数不确定的循环语句

D:初始化语句initial

答案: 【

】

5、单选题:

对行为描述always语句块的说法中,正确的是( )

选项:

A:边沿触发的方式用来描述时序逻辑电路,将生成锁存器结构

B:边沿触发方式中,对同一个时钟,可以同时混合使用其上升沿和下降沿

C:利用电平触发的方式可以描述组合逻辑电路,且建议采用阻塞性过程赋值

D:可以在两个或两个以上的always语句块中对同一个变量赋值

答案: 【

】

第十二章 单元测试

1、判断题:

在数字系统设计的过程中,设计者首先对所设计的系统要有一个全面的理解,然后从顶层开始,连续地逐层向下分解,直到系统的所有模块都小到便于掌握为止。这种方法叫做自底向上的设计实现。( )

选项:

A:对

B:错

答案: 【】

2、判断题:

在数字系统设计的过程中,完成各个子模块的编程之后,还需要编写一个模块,该模块含有所有子模块的连接关系的信息,一般称为顶层模块。( )

选项:

A:错

B:对

答案: 【】

3、单选题:

在动态扫描显示电路中,不需要用到的电路模块是( )

选项:

A:编码器模块

B:循环移位扫描模块

C:选择器模块

D:七段显示译码模块

答案: 【

】

4、单选题:

在一般的只读存储器模块中,除了时钟、复位、读写控制端口和数据输出端口外,还必须有( )

选项:

A:置位端口

B:数据输入端口

C:地址输出端口

D:地址输入端口

答案: 【

】

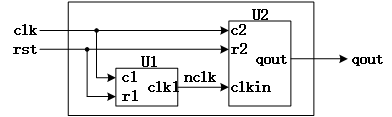

5、单选题:

为了完成如图所示数字系统,假设已经完成模块U1(模块名称div)和U2(模块名称mymodule)的编程:

则在顶层模块中调用两个子模块的格式可能正确的是( )

选项:

A:div U1 (clk,rst,clk1);

mymodule U2(clk,rst,clkin,qout);

B:div U1 (clk,rst,nclk);

mymodule U2(clk,rst,nclk,qout);

C:div U1 (c1,r1,clk1);

mymodule U2(c2,r2,clkin,qout);

D:div (c1,r1,clk1);

mymodule(c2,r2,clkin,qout);

答案: 【

】

第十三章 单元测试

1、判断题:

在可编程逻辑器件的基本结构中,输入输出缓冲电路的作用是产生输入信号的原变量和反变量,并增强输入信号的驱动能力。( )

选项:

A:错

B:对

答案: 【】

2、判断题:

可编程逻辑器件是一类实现逻辑功能的通用器件,其内部由逻辑门和可编程开关构成,因此只能实现组合逻辑电路,不能实现时序逻辑电路。( )

选项:

A:错

B:对

答案: 【】

3、单选题:

复杂可编程逻辑器件主要有CPLD和FPGA两类,下列对FPGA的结构与工作原理的描述,正确的是( )

选项:

A:FPGA的是基于乘积项结构的可编程逻辑器件

B:一般情况下,FPGA比CPLD更加适合完成组合逻辑电路

C:FPGA全称为复杂可编程逻辑器件

D:基于SRAM的FPGA器件,在每次上电后必须进行一次配置

答案: 【

】

4、单选题:

复杂可编程逻辑器件主要有CPLD和FPGA两类,其中CPLD中实现逻辑功能的主体部分是( )

选项:

A:查找表(LUT)

B:输出缓冲

C:可编程乘积项逻辑

D:输入缓冲

答案: 【

5、单选题:

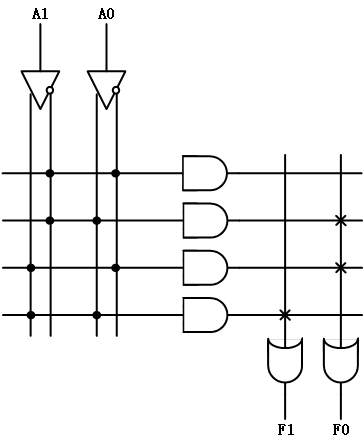

如下图所示的逻辑阵列中,

输出F0实现的逻辑功能是( )

选项:

A:F0=A1&A0

B:F0=A1|A0

C:F0=A1+A0

D:F0=A1^A0

答案: 【

】

请先 !