第一章 单元测试

1、单选题:

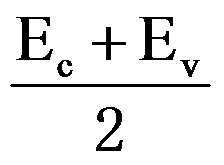

本征硅的费米能级位于:( )

选项:

A:

B: 略偏向

略偏向

C: 略偏向

略偏向

D:

答案: 【 略偏向

略偏向

】

2、单选题:

硼掺杂的硅中,下列说法正确的是:( )

选项:

A:空穴浓度大于电子浓度

B:电子浓度大于空穴浓度

C:硅的晶体结构将发生改变

D:与磷掺杂硅的导电类型一致

答案: 【空穴浓度大于电子浓度

】

3、多选题:

抑制离子注入工艺中沟道效应的方法有( )。

选项:

A:降低离子注入能量

B:衬底表面沉积非晶薄膜

C:升高衬底温度

D:倾斜衬底

答案: 【衬底表面沉积非晶薄膜

;升高衬底温度

;倾斜衬底

】

4、多选题:

制造单晶硅衬底的方法包括( )。

选项:

A:直拉法

B:外延生长法

C:区域熔融法

D:氧化还原法

答案: 【直拉法

;区域熔融法

】

5、判断题:

当硅中掺杂浓度越小时,费米能级越靠近Ei。( )

选项:

A:错

B:对

答案: 【对】

第二章 单元测试

1、多选题:

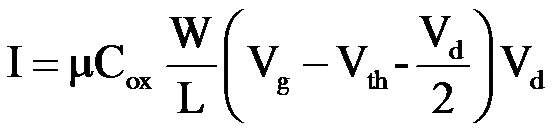

对于长沟道MOSFET器件,发生夹断后,下面说法中正确的是( )。

选项:

A:Vg继续增加,Id不会继续增大

B:沟道中漏极一侧的电位为0

C:

D:Vg≥Vd+Vth

答案: 【Vg继续增加,Id不会继续增大

;沟道中漏极一侧的电位为0

;Vg≥Vd+Vth

】

2、多选题:

沟道长度缩短有可能对MOSFET器件产生哪些影响( )。

选项:

A:阈值电压增大

B:器件的集成度增加

C:器件的漏极电流增大

D:器件的可靠性劣化

答案: 【器件的集成度增加

;器件的漏极电流增大

;器件的可靠性劣化

】

3、单选题:

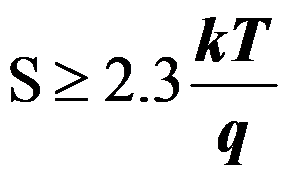

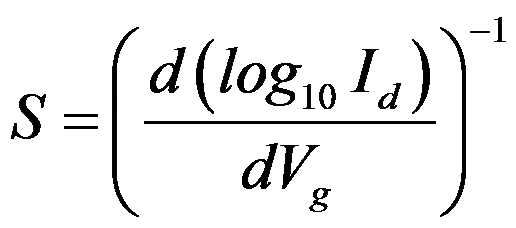

有关MOSFET器件亚阈值摆幅(S)的说法错误的是( )

选项:

A:

B:温度升高,亚阈值摆幅增大

C:亚阈值摆幅的单位是mV

D:

答案: 【亚阈值摆幅的单位是mV

】

4、单选题:

有关MOSFET器件特征长度的说法正确的是( )

选项:

A:仅与器件的结构参数有关

B:沟道长度相等的器件,特征长度越小,DIBL越小

C:与器件的沟道长度呈正比

D:栅氧化层介电常数越厚,特征长度越小

答案: 【沟道长度相等的器件,特征长度越小,DIBL越小

】

5、判断题:

MOSFET器件的阈值电压实际上是栅极MOS电容强反型区的起点。( )

选项:

A:对

B:错

答案: 【对】

第三章 单元测试

1、多选题:

下面有关浸没式光刻技术的说法,正确的是( )

选项:

A:能够增大物镜的数值孔径

B:由台积电的工程师林本坚发明

C:在目镜和衬底间填充水

D:能够减小光的波长

答案:

2、多选题:

相移光刻技术中,使光产生相位差的方法包括:( )

选项:

A:在掩膜板上的透光区域中添加移相器

B:减小未沉积铬区域的石英板厚度

C:利用整面透光的石英板,改变局部区域的厚度

D:改变石英掩膜板的倾斜角

答案:

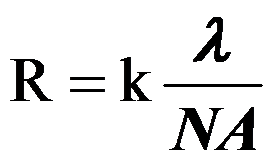

3、单选题:

根据瑞利判据得到的光刻分辨率极限,表达式为( )

选项:

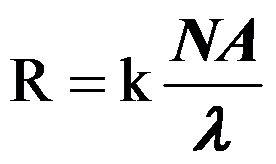

A:

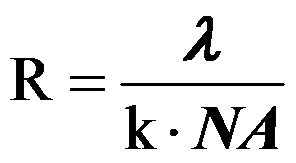

B:

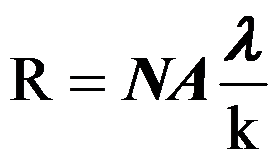

C:

D:

答案:

4、单选题:

正光刻胶和负光刻胶中,光敏剂的作用分别是( )

选项:

A:交联催化剂,交联催化剂

B:交联催化剂,提供自由基

C:提供自由基,提供自由基

D:提供自由基,交联催化剂

答案:

5、判断题:

光刻是集成电路制造过程中总成本最高的工艺。( )

选项:

A:错

B:对

答案:

第四章 单元测试

1、多选题:

有关半导体中载流子有效质量的说法正确的是( )

选项:

A:受到半导体晶格周期性势场的影响

B:与载流子的惯性质量在数值上相等

C:具有一定的概率分布

D:电子和空穴可能具有不同的有效质量

答案:

2、多选题:

张应变和压应变影响硅沟道中载流子迁移率的共同原因有( )

选项:

A:减小载流子有效质量

B:减小MOS界面粗糙度

C:增加能级分裂,抑制能谷散射

D:抑制界面态的库伦散射作用

答案:

3、单选题:

在硅沟道场效应晶体管器件中,埋入式源漏技术能够产生何种应变( )

选项:

A:既有可能产生张应变,又有可能产生压应变

B:其余选项说法都不对

C:仅能产生压应变

D:仅能产生张应变

答案:

4、单选题:

对于高集成密度的n型沟道的Si FinFET器件,合适的产生应变的技术是( )

选项:

A:应力记忆技术

B:SiGe虚拟衬底技术

C:SiGe埋入式源漏技术

D:接触式刻蚀中止层技术

答案:

5、判断题:

应变硅技术从90纳米技术节点开始进入量产。( )

选项:

A:对

B:错

答案:

第五章 单元测试

1、多选题:

有关High-k/metal gate技术的说法正确的是( )

选项:

A:能够减小栅氧化层中的电场强度

B:栅氧化层k值越大越好

C:能够提升沟道中的载流子迁移率

D:从45纳米技术节点开始进入量产

答案:

2、多选题:

作为High-k栅氧化层的材料,需要具备下面哪些特点( )

选项:

A:需要是常见材料

B:需要具有较高的k值

C:需要具有合适的能带结构

D:需要具有较好的稳定性

答案:

3、多选题:

下面哪种方法能够减小Si栅极堆垛的EOT( )

选项:

A:利用high-k材料替代二氧化硅栅绝缘层

B:减薄栅绝缘层的厚度

C:应用Scavenging技术

D:利用金属栅替代多晶硅栅

答案:

4、判断题:

几种薄膜沉积方法中,三维表面包覆能力由强到弱依次为:ALD、PECVD、电子束蒸镀。( )

选项:

A:对

B:错

答案:

5、判断题:

Scavenging技术实质上是氧化还原反应。( )

选项:

A:对

B:错

答案:

第六章 单元测试

1、多选题:

根据传输线模型,有关场效应晶体管器件源漏接触电阻的说法正确的是( )

选项:

A:源漏接触电极越大,接触电阻一定越小

B:分为长接触极限和短接触极限两种特例

C:源漏接触金属下方的电流密度不均匀

D:与金属的功函数无关

答案:

2、多选题:

当互联的最小特征尺寸减小时,下面说法错误的是( )

选项:

A:互联延时增大

B:互联延时减小

C:互联寄生电容不变

D:互联寄生电阻增大

答案:

3、单选题:

Al互联中不包含下面那个结构( )

选项:

A:Liner

B:Al配线

C:W通孔

D:Cu通孔

答案:

4、单选题:

下面哪种方法不能抑制场效应晶体管器件中的寄生电容( )

选项:

A:空气侧墙

B:后栅工艺

C:high-k栅绝缘层

D:引入沟道应变

答案:

5、判断题:

特征尺寸越小,栅极延迟和互联延时都越小。( )

选项:

A:错

B:对

答案:

评论0